El año pasado se informó que los fabricantes de DRAM, incluidos Samsung, SK Hynix y Micron, ya comenzaron el desarrollo de DDR6, centrándose en el diseño de chips, la verificación de controladores y la integración de módulos de paquetes. Los fabricantes de DRAM han completado el diseño de los prototipos de chips DDR6 y están trabajando con fabricantes de plataformas y controladores de memoria como Intel y AMD para realizar pruebas de interfaz.

Según The Elec, los fabricantes de DRAM como Samsung, SK Hynix y Micron han coordinado recientemente el desarrollo de módulos de memoria DDR6 con proveedores de sustratos, incluido el grosor, la estructura de apilamiento y el cableado. Actualmente se están produciendo y verificando productos prototipo DDR6, y este trabajo también se lleva a cabo bajo la supervisión de la Asociación de Tecnología de Estado Sólido JEDEC.

JEDEC proporciona un borrador preliminar de DDR6 en 2024, logrando avances significativos en rendimiento y arquitectura. Cambia a un diseño multicanal y utiliza subcanales de 4×24 bits, que es diferente de la configuración de 2×32 bits de DDR5. Esto traerá un mejor procesamiento paralelo, flujo de datos y utilización del ancho de banda y, por supuesto, también plantea requisitos más altos para el diseño de E/S del módulo y la integridad de la señal. Se espera que las velocidades de

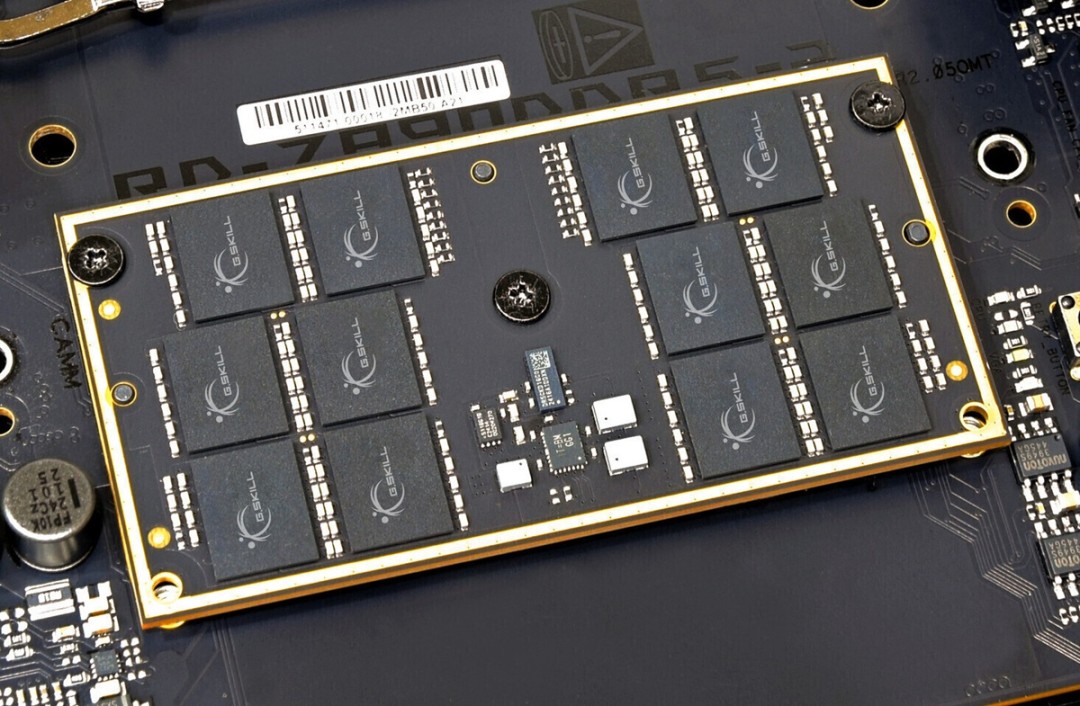

DDR6 comiencen en 8,8 Gbps, aumenten hasta 17,6 Gbps e incluso puedan ampliarse a 21 Gbps. Al mismo tiempo, DDR6 admite el nuevo estándar CAMM2, que reemplaza los estándares SO-DIMM y DIMM utilizados desde hace mucho tiempo, proporcionando mayor ancho de banda, mayor densidad, menor impedancia y un factor de forma más delgado, y también resuelve las limitaciones físicas de las ranuras de memoria tradicionales.

En la actualidad, la industria ha completado la transición a DDR5. El año pasado representó más del 80% del mercado de servidores y se espera que alcance el 90% este año. Originalmente, JEDEC podría haber lanzado la especificación estándar DDR6 antes, pero algunas especificaciones importantes no se han finalizado, incluido el grosor, el uso de la señal, el rango de potencia y el diseño de los pines. Esto cambiará a medida que los fabricantes de DRAM aceleren el desarrollo de productos estándar DDR6, cuya comercialización se espera entre 2028 y 2029.