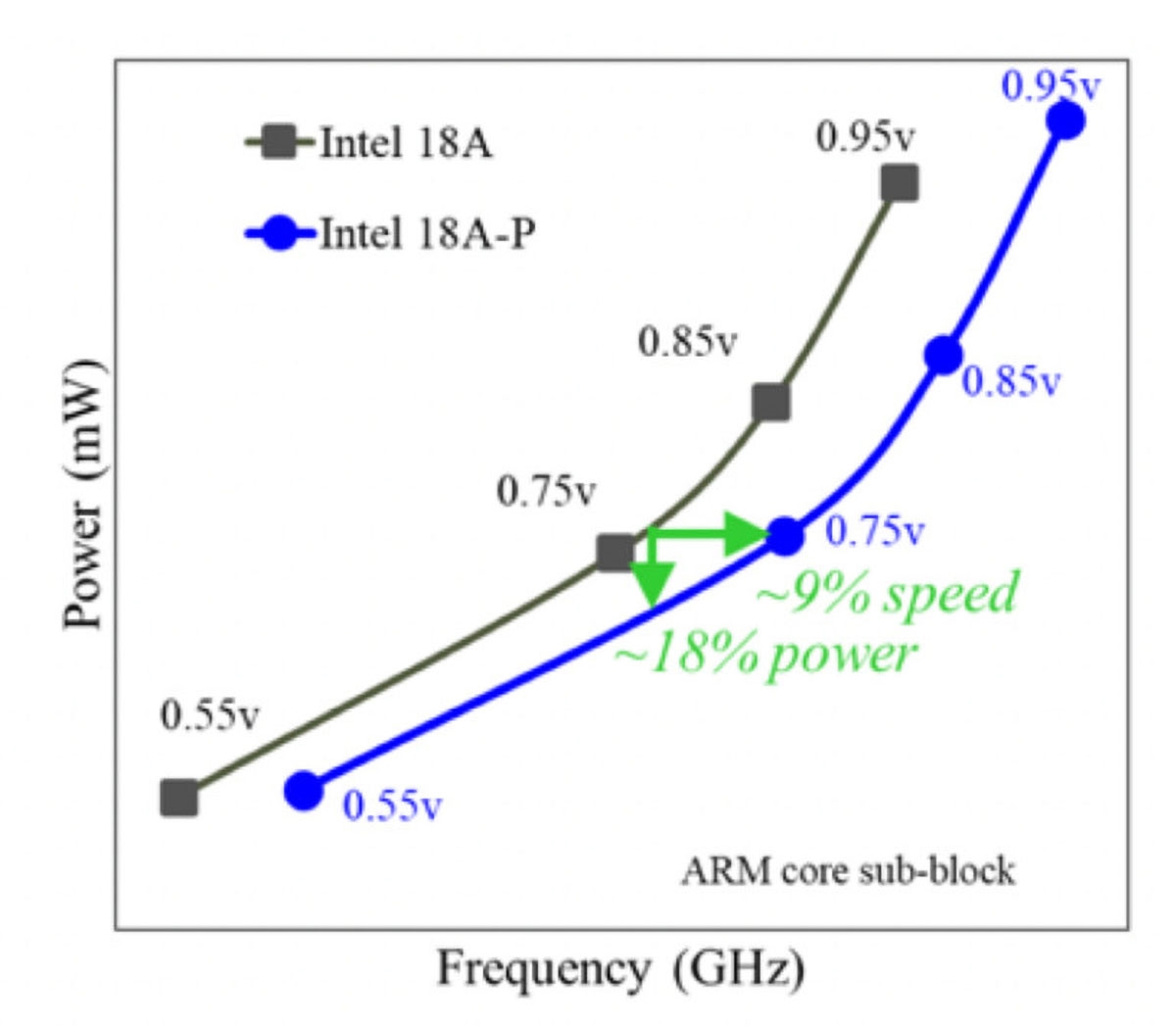

Intel anunció oficialmente los datos técnicos clave del nodo de proceso Intel 18A-P a través del documento T1.2 en el seminario VLSI 2026 celebrado en Honolulu, Hawaii. En comparación con el nodo Intel 18A estándar, el 18A-P logra una ganancia de rendimiento de más del 9 % con el mismo consumo de energía y reduce el consumo de energía en más del 18 % con el mismo rendimiento.

Este tipo de mejoras de rendimiento y potencia, que normalmente solo se ven con transiciones de nodos intergeneracionales, ahora se pueden lograr con el 18A-P con la misma densidad.

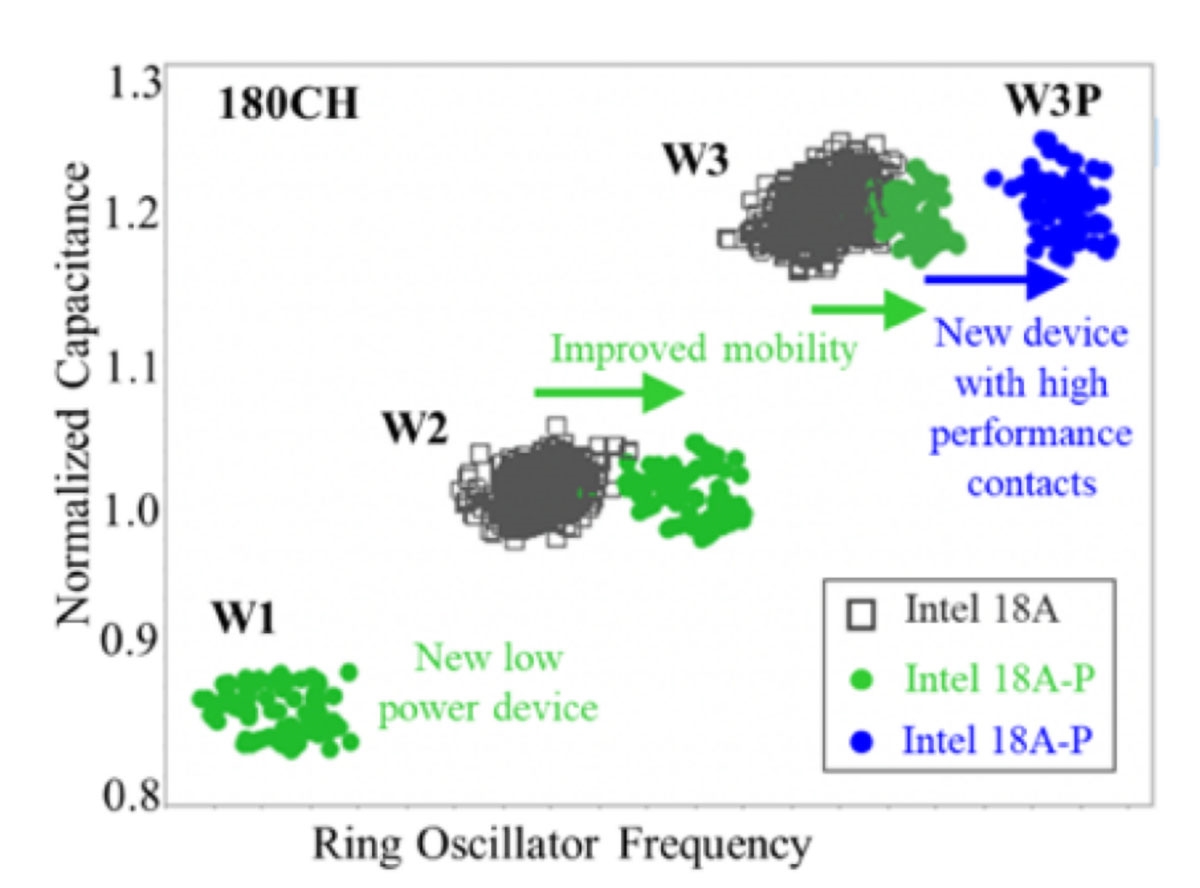

El documento original de Intel enumera cuatro mejoras específicas: pares lógicos VT adicionales, control más estricto del ángulo de compensación del reloj, nuevos dispositivos de bajo consumo en bibliotecas de alta densidad (HD) y alto rendimiento (HP), y versiones de rendimiento mejorado de dispositivos HP en ambas bibliotecas.

Intel ha reducido las esquinas sesgadas del 18A-P en aproximadamente un 30% en comparación con el 18A estándar. La diferencia de rendimiento entre transistores en la misma oblea se reduce significativamente, el consumo de energía y las características de rendimiento son más predecibles y, al mismo tiempo, se mejoran el rendimiento de los parámetros y la consistencia del chip.

En términos de disipación de calor, la resistencia térmica del 18A-P es aproximadamente un 50% menor que la del 18A y la eficiencia de la conductividad térmica mejora considerablemente. Esto es particularmente crítico para el funcionamiento sostenido de alta frecuencia en escenarios informáticos de alto rendimiento y también responde directamente a los desafíos de disipación de calor que plantea la tecnología de suministro de energía trasera (PowerVia).

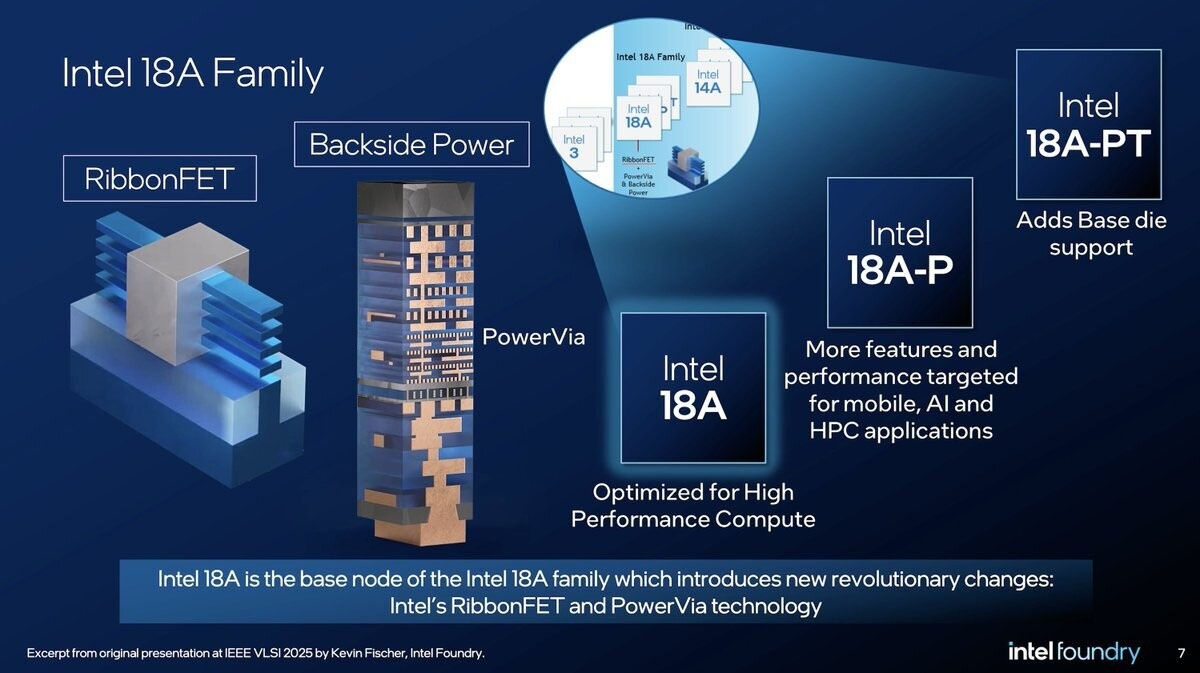

Intel ha enviado la versión 1.0 de su kit de diseño de procesos PDK para 18A-P a clientes potenciales para permitirles comenzar a probar la verificación del chip. Este proceso todavía se basa en la arquitectura de transistor de puerta integral RibbonFET y la tecnología de fuente de alimentación trasera PowerVia, y es una versión de rendimiento mejorado de la plataforma 18A.

Según TrendForce, Apple está evaluando el uso del proceso 18A-P para producir chips de la serie M, mientras que Google está considerando utilizar la tecnología de empaquetado avanzada EMIB de Intel para promover el proyecto TPU v8e. Es posible que los productos relacionados se lancen a partir de 2027.